آزمایش ویفر

مرحلهای که درطول برساخت افزاره نیمرسانا با اعمال الگوهای آزمایشی خاص روی ویفر قبل از ارسال به آمایش دای انجام میشود.

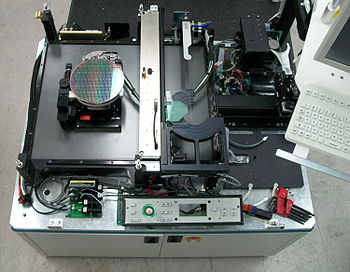

آزمایش ویفر (به انگلیسی: Wafer testing) مرحلهای است که در طول ساخت افزارههای نیمرسانا انجام میشود. در طی این مرحله، قبل از ارسال ویفر برای آمایش دای، تمام مدارهای مجتمع مجزا که روی ویفر وجود دارند با اعمال الگوهای آزمایشی ویژه برروی آنها از نظر نقص عملکردی آزموده میشوند. آزمایش ویفر توسط قطعهای از تجهیزات آزمایشی به نام کاونده ویفر انجام میشود. فرایند آزمایش ویفر را میتوان به چند طریق ذکر کرد: آزمایش نهایی ویفر (WFT)، جورکردن دای الکترونیکی (EDS) و پروب مدار (CP) احتمالاً رایجترین آنها هستند.

کاونده ویفر همچنین هرگونه مدارات آزمون را روی خطوط نشانهگذاری (به انگلیسی: scribe lines) ویفر اعمال میکند. برخی از شرکتها بیشتر اطلاعات خود را در مورد عملکرد قطعه از این ساختارهای آزمون خط نشانهگذاری بهدست میآورند.[۱][۲][۳]

جستارهای وابسته

ویرایشمنابع

ویرایش- ↑ "Startup enables IC variability characterization" بایگانیشده در ۱۶ سپتامبر ۲۰۱۶ توسط Wayback Machine by Richard Goering 2006

- ↑ "Testing LCD Source Driver IC with Built-on-Scribe-Line Test Circuitry" (abstract)

- ↑ Design for Manufacturability And Statistical Design: A Constructive Approach, by Michael Orshansky, Sani Nassif, Duane Boning 2007. شابک ۰−۳۸۷−۳۰۹۲۸−۴ شابک ۹۷۸−۰−۳۸۷−۳۰۹۲۸−۶ p. 84

کتابشناسی - فهرست کتب

ویرایش- مبانی آزمایش نیمرسانای دیجیتال (نسخه ۴٫۰) توسط گای ای پری (محصول مارپیچی - ۱ مارس ۲۰۰۳)شابک ۹۷۸–۰۹۶۵۸۷۹۷۰۵

- اصول آزمایش شبکه نیمرسانا (آزمایش و اندازهگیری) (جلد گالینگور) اثر امیر افشار، ۱۳۷۴شابک ۹۷۸-۰-۷۵۰۶-۹۴۷۲-۸

- آزمایش توان-محدود مدارهای VLSI. راهنمای استاندارد آزمون IEEE 1149.4 (مرزها در آزمایش الکترونیکی) توسط نیکولا نیکولیچی و بشیر ام. الهاشمی (نسخه کیندل – ۲۸ فوریه ۲۰۰۳)شابک ۹۷۸-۰-۳۰۶-۴۸۷۳۱-۶

- حافظههای نیمرسانا: فناوری، آزمایش و قابلیت اطمینان توسط آشوک کی شارما (جلد گالینگور – ۹ سپتامبر ۲۰۰۲)شابک ۹۷۸–۰۷۸۰۳۱۰۰۰۱